# High performance PWM Power Switch IC

#### 1. Feature

Meet DoE VI and CoC V5 energy efficiency requirements

Built-in 700V BVdss MOSFET power switch

No load standby power consumption as low as 50 mW

Built-in oscillator with maximum 65 kHz frequency limit

Built-in soft start control circuit reduces switch impact

Built-in second-generation C.T.<sup>TM</sup> technology optimizes EMI performance

Extended mode light load control for optimized efficiency and light load power

Full range of no audio noise working methods

Integrated synchronous current ramp compensation

VDD overvoltage clamp and undervoltage lockout (UVLO)

Gate drive output voltage smart clamp function

Built-in input line voltage compensation

Cycle-by-Cycle Current Limiting with Leading Edge Blanking (OCP)

Output overcurrent, overload, short circuit protection (OLP)

Wide voltage output power up to 25W, peak power is 35W

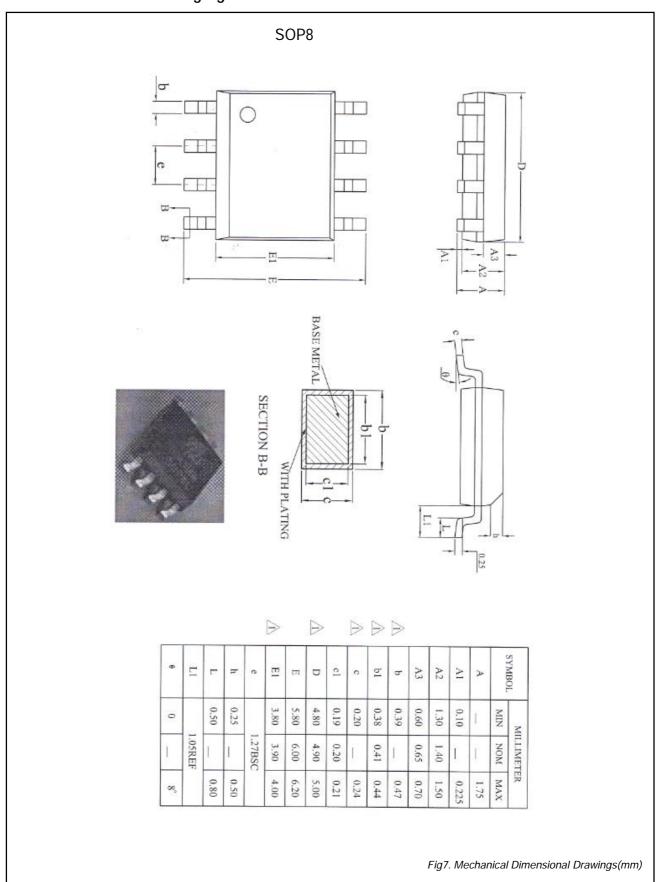

Available in a highly isolation SOP8 package and meets the green halogen-free requirements

## 2. Applications

Power Adapter

**Battery Charger**

**Quick Charger**

Open-frame Power

## 3. Description

The LN9T27DH/EH is a high performance, highly integrated current mode PWM controller that makes it easy to build low standby power, low cost, high performance solutions to meet CoC V5 and DoE VI energy efficiency in applications. The PWM switching frequency is internally set by the chip and has full temperature compensation. The maximum value is set at 65 kHz. Under no-load or light load conditions, the IC can operate in intelligent interrupt mode to reduce switching losses, so it can be achieved good conversion efficiency while having lower standby power consumption. The low VDD startup current and operating current allow the LN9T27DH/EH to have very high reliability and longevity. A resistor with larger resistance can be used to complete the circuit startup, which also reduces the loss of the startup resistor, further reduces the system standby power. The built-in current ramp compensation greatly optimizes the reliability of the circuit over large PWM duty cycles and avoids subharmonic oscillations that may occur. The built-in leading edge blanking circuit avoids the inductance turn-on current spike interference with current sampling and the effect on the snubber diode reverse recovery current, and the external no longer requires an additional blanking circuit. The LN9T27DH/EH also offers a very

comprehensive protection circuit with auto-recovery, including cycle-by-cycle current limit (OCP), output overload protection (OLP) with high and low voltage compensation, VDD overvoltage protection and undervoltage lockout (UVLO).

Based on the new smartEnergy<sup>™</sup> technology from Lii Semi, the system standby power and light load efficiency are greatly improved. The conversion efficiency can meet the CoC and DoE VI energy efficiency requirements in general application, and the no-load power can be as low as 50 mW or less.

By incorporating the unique second-generation C.T.<sup>TM</sup> patented technology from Lii Semi into the output pulse with specially designed output soft clamp totem pole technology, the EMI characteristics of the system have been greatly improved and can easily meet the electromagnetic compatibility standards of various countries.

Highly isolated standard SOP8 green packages are available.

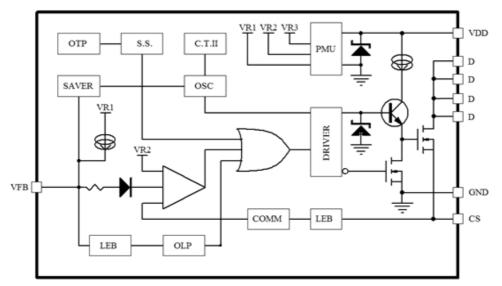

## 4. Functional Block Diagram

Fig1. Internal functional block diagram

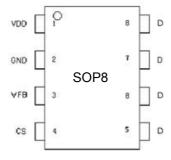

#### 5. Pin Definitions

Fig2. Pin Definitions

## 6. Pin Function Description

| PIN     | Symbol | Function                                                                                   |

|---------|--------|--------------------------------------------------------------------------------------------|

| 1       | VDD    | Power supply pin, connect the starting resistor and auxiliary power supply circuit         |

| 2       | GND    | Ground pin                                                                                 |

| 3       | VFB    | Feedback signal input pin, connected to output feedback signal (optocoupler)               |

| 4       | CS     | Switch current sense signal input pin, connected to the current limit resistor             |

| 5,6,7,8 | D      | The high-voltage MOSFET switch's drain pin, which connects the transformer primary winding |

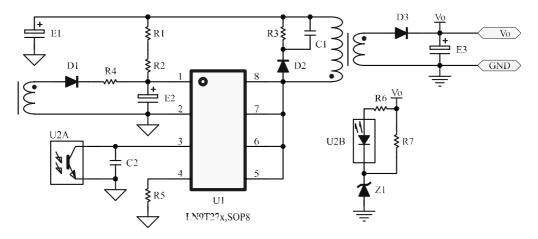

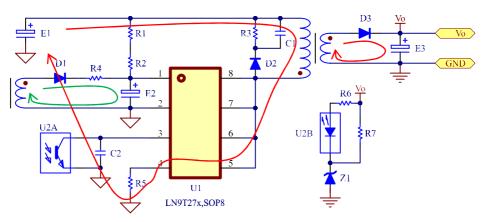

## 7. Typical Simplified Schematic

Fig3. Typical Simplified Schematic

## 8. Absolute Maximum Ratings \*

| Parameter |                                  | Rating         | Units       |    |

|-----------|----------------------------------|----------------|-------------|----|

|           | D Pin Voltage                    |                | 700**       | V  |

| D Die le  | and Command                      | LN9T27DH       | 6***        | A  |

| D PIN IN  | put Current                      | LN9T27EH       | 9***        | A  |

|           | VDD Pin Volta                    | ge             | 40**        | V  |

|           | Other Pin Volta                  | age            | -0.3 to +7  | V  |

|           | PD                               |                | 1000        | mW |

| Min/Max C | perating Junction                | Temperature TJ | -40 to +150 | °C |

| Min/Max C | perating Ambient                 | Temperature Ta | -20 to +125 | °C |

| Min/M     | lax Storage Temp                 | erature Tstg   | -55 to +150 | °C |

| Recon     | Recommended Soldering Conditions |                | 260℃ , 10S  |    |

| FCD       | ESD HBM MM                       |                | 2500        | V  |

| ESD       |                                  |                | 250         | V  |

Note\*: Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum-rated conditions for ex tended periods may affect device reliability. \*\*: With 10 mA limit. \*\*\*: Only allow 1 ms pulse and period is 1 s.

## 9. Recommended Operating Conditions

| Symbol | Parameter             |                               | Min | Тур | Max | Units |

|--------|-----------------------|-------------------------------|-----|-----|-----|-------|

| VDD    | VDD Supply Volt       | VDD Supply Voltage            |     |     | 38  | V     |

| Vds    | Drain Peak Volta      | Drain Peak Voltage            |     | -   | 650 | V     |

| lde    | Dunin Book Commont    | LN9T27DH                      | -   | -   | 2.5 | А     |

| Ids    | Drain Peak Current    | LN9T27EH                      | -   | -   | 3.5 | А     |

| TA     | Operating Ambient Ter | Operating Ambient Temperature |     | -   | 105 | °C    |

## 10. Electrical Characteristics(Ta = 25 °C, VDD=15V, if not otherwise noted)

## MOSFET Section (Drain Pin)

| Symbol            | Parameter            | Test Co                                               | nditi                                                 | ons                   | Min | Тур | Max | Units |

|-------------------|----------------------|-------------------------------------------------------|-------------------------------------------------------|-----------------------|-----|-----|-----|-------|

| BV <sub>DSS</sub> | Drain-Source Voltage | VDD=0 V,                                              | , I <sub>D</sub> =                                    | 1 mA                  | 700 | -   | i   | V     |

| I <sub>HV</sub>   | D-S Leakage Current  | V <sub>D</sub> =6                                     | 90 \                                                  | /                     | -   | -   | 10  | uA    |

| В                 | MOCEET DAGON         | I <sub>D</sub> =1.5 A, T <sub>J</sub> =25 °           | С                                                     | LN9T27DH              | -   | 1.5 | -   | Ω     |

| R <sub>DSON</sub> | MOSFET RdsON         | I <sub>D</sub> =2.5 A, T <sub>J</sub> =25 °           | I <sub>D</sub> =2.5 A, T <sub>J</sub> =25 °C LN9T27EH |                       | -   | 1.0 | -   | Ω     |

| T <sub>R</sub>    | Switch Rise Time     | CL=1                                                  | mŀ                                                    | 1                     | -   | 35  | -   | nS    |

| $T_F$             | Switch Fall Time     | CL=1                                                  | mŀ                                                    | 1                     | -   | 35  | 1   | nS    |

|                   |                      | I NOTOZDU                                             |                                                       | T <sub>J</sub> =25 °C | -   | 6   | -   | Α     |

|                   | Drain Current Duland | LN9T27DH T <sub>J</sub> =125 °C T <sub>J</sub> =25 °C |                                                       | -                     | 2.5 | -   | Α   |       |

| I <sub>D</sub>    | Drain Current Pulsed |                                                       |                                                       | T <sub>J</sub> =25 °C |     | 9   |     | Α     |

|                   |                      | LINST2/EM                                             | LN9T27EH T <sub>J</sub> =125 °C                       |                       |     | 3.5 |     | Α     |

### **VDD** Section

| Symbol             | Parameter                   | Test Conditions         | Min | Тур | Max | Units |

|--------------------|-----------------------------|-------------------------|-----|-----|-----|-------|

| I <sub>QS</sub>    | VDD Startup Current         | VDD=15 V                | -   | 1   | 10  | uA    |

| IQ                 | Operating Current           | VDD=16 V,VFB=OPEN       | -   | 1.2 | -   | mA    |

| V <sub>STOP</sub>  | IN/I O Three should Veltage | ED-0                    | 6.5 | 7   | 8   | V     |

| V <sub>START</sub> | UVLO Threshold Voltage      | FB=0                    | -   | 17  | -   | V     |

| V <sub>OVP</sub>   | VDD OVP Threshold           |                         | -   | 39  | -   | V     |

| VDD_CL             | VDD Clamp Voltage           | I <sub>VDD</sub> =10 mA | -   | 40  | -   | V     |

### **OSC Section**

| Symbol               | Parameter                                               | Test Conditions               | Min | Тур | Max | Unit |

|----------------------|---------------------------------------------------------|-------------------------------|-----|-----|-----|------|

| Fosc                 | OSC Switching Frequency                                 |                               | 60  | 65  | 70  | kHz  |

| ΔF <sub>OSC</sub> _T | F <sub>OSC</sub> VS Ta                                  | VDD=16 V, Ta=-20 °C to 100 °C | -   | 5   | -   | %    |

| ΔF <sub>OSC</sub> _V | F <sub>OSC</sub> _V F <sub>OSC</sub> VS VCC VDD=12-25 V |                               | -   | 5   | -   | %    |

| F <sub>OSC_MIN</sub> | Min. Burst Mode frequency                               | VDD=16 V                      | -   | 22  | -   | kHz  |

### VFB Section

| Symbol             | Parameter                         | Test Conditions          | Min | Тур  | Max | Units |

|--------------------|-----------------------------------|--------------------------|-----|------|-----|-------|

| $V_{FB}$           | VFB Open Loop Voltage             | V <sub>FB</sub> is open  |     | 4.6  |     | V     |

| I <sub>FB_S</sub>  | FB Short Circuit Current          | FB=0                     |     | 0.20 |     | mA    |

| VTH <sub>MIN</sub> | Zero Duty Cycle Threshold Voltage | VDD=16 V                 |     | 0.75 |     | V     |

| VTH <sub>MAX</sub> | Power Limit Threshold<br>Voltage  | VDD=16 V                 |     | 3.7  |     | V     |

| T <sub>OLPI</sub>  | Power Limit Delay Time            | VDD=16 V                 |     | 85   |     | mS    |

| D <sub>MAX</sub>   | Max. Duty Cycle                   | VDD=16 V, FB=3.3 V, CS=0 |     | 80   |     | %     |

### **CS Section**

| Symbol             | Parameter                 | Test Conditions                           | Min | Тур  | Max | Units |

|--------------------|---------------------------|-------------------------------------------|-----|------|-----|-------|

| T <sub>LEB</sub>   | L.E.B Time                |                                           | -   | 250  | -   | nS    |

| Z <sub>CS</sub>    | CS Input Resistance       |                                           | -   | 40   | -   | ΚΩ    |

| T <sub>OCP</sub>   | OCP Delay Time            | VDD=16 V,V <sub>CS</sub> >VTH_OC,FB=3.3 V | -   | 75   | -   | nS    |

| VTH <sub>OCP</sub> | Max. CS Threshold         | FB=3.3V                                   | -   | 0.75 | -   | V     |

| T <sub>SS</sub>    | Internal Soft Start Delay |                                           | -   | 12   | -   | mS    |

| VTH <sub>OSP</sub> | OSP Threshold Voltage     |                                           | -   | 1.45 | -   | V     |

## $Cycleturning^{TM}II\ (C.T.II)\ Section$

| Symbol            | Parameter  | Test Conditions | Min | Тур | Max | Unit |

|-------------------|------------|-----------------|-----|-----|-----|------|

| ΔF <sub>OSC</sub> | C.T. Range |                 | -   | ±4  | -   | %    |

| T <sub>CT</sub>   | C.T. Time  |                 | -   | 4   | -   | mS   |

## **OTP Section**

| Symbol             | Parameter      | Test Conditions | Min | Тур | Max | Unit       |

|--------------------|----------------|-----------------|-----|-----|-----|------------|

| ОТР                | ОТР            |                 | -   | 145 | -   | ℃          |

| OTP <sub>HYT</sub> | OTP hysteresis |                 | -   | 30  | -   | $^{\circ}$ |

#### **Thermal Data**

| Symbol                       | Parameter                           | Rating | Unit |

|------------------------------|-------------------------------------|--------|------|

| $\theta_{JA}^{-1}$           | Thermal Resistance Junction-Ambient | 90     | °C/W |

| θ <sub>JC</sub> <sup>2</sup> | Thermal Resistance Junction-Case    | 25     | °C/W |

Notes: 1. All leads are soldered on a 250 mm<sup>2</sup> copper foil with 2 oz thick to measuring. 2. Measured on the surface of the package near pin 7.

11. This is a blank page.

## 12. Application and Implementation

The LN9T27DH/EH is a highly integrated PWM control IC that is optimized for 30 W off-line applications. Its high-efficiency Burst mode control greatly reduces standby loss, improves conversion efficiency at light loads, and easily meets international energy efficiency standards such as CoC V5 and DoE VI.

#### 12.1 Start-up current and start-up control

The LN9T27DH/EH can operate at very low start-up current conditions, with accurate UVLO control enabling fast and reliable power-up in a short period of time. Allowing a large start-up resistor value can significantly reduce the start-up power consumption, such as 3 M $\Omega$ , although a 1/8W power-class resistor can meet the required power requirements, but must still carefully consider its ability to withstand voltage, The use of resistors in series is recommended, for example, using two 1206-type chip resistors in series.

The start-up resistor can be connected between AC input terminal or the positive of input DC high voltage and the VDD storage capacitor.

#### 12.2 Operating current and VDD capacitance

The normal operating current of LN9T27DH/EH is as low as 1.2 mA. The loss of the IC itself is small during operation. An electrolytic capacitor with capacity of not less than 4.7 uF can meet the sufficient energy required for IC power supply and driving, but consider the larger input capacitance of MOSFET and the wider operating temperature range, a lower internal resistance (ESR) type of the capacitor should be chosen to provide fast and large current when the MOSFET is turned on, speeding up MOSFET turn-on.

#### 12.3 Cycleturning™ II (C.T. II)

The LN9T27DH/EH integrates the optimized second-generation Cycleturning<sup>™</sup> proprietary technology from the clock cycle is modulated at the set time in the work process, resulting in a larger switching pulse spectrum to reduce the narrowband energy density, so that the average interference intensity in any single bandwidth is greatly reduced. Therefore, the cost of the system on EMI is also greatly reduced.

#### 12.4 Extended BM operating characteristics

Under no-load or light-load conditions, the ratio of the total loss of MOSFET switching losses will increase significantly, and the switching loss is proportional to the switching frequency. Lowering the switching frequency can significantly reduce the switching losses of the MOSFET. LN9T27DH/EH by detecting the FB voltage and time size, the system no-load or light load will automatically adjust the switching frequency to a lower value, the more FB voltage is lower than the set control voltage, the more the frequency decreases, but the circuit automatically limits the minimum value of the frequency drop above 22 kHz to avoid audible noise.

When the system frequency drops to near 22 kHz, if the FB voltage is still lower than the set threshold voltage, the output will be disabled to ensure that the output voltage will not be too high.

#### 12.5 Current detection and leading edge blanking

The LN9T27DH/EH provides cycle-by-cycle current limiting, and the switching current is sampled into the IC through the current limiting resistor. The built-in leading-edge blanking eliminates current spikes into the IC, avoid the current limit function malfunction, the MOSFET will not be turned off by mistake, so the traditional external blanking circuits will no longer be needed.

The duty cycle of the PWM is determined by the combination of the sampling current and the FB voltage. The typical threshold voltage of the overcurrent comparator when FB is floating is 0.75 V.

#### 12.6 Synchronous slope compensation

The IC integrates a voltage slope that is synchronized with the clock to the compensation circuit of the current sampling signal, which greatly improves the infinite loop stability of the circuit at large duty cycles and CCM, prevents possible subharmonic oscillation problems, and enhances output voltage stability.

#### 12.7 Output power switch

The LN9T27DH/EH integrates a MOSFET power switch BVdss voltage up to 700 V. The power switch has extremely low RdsON internal resistance and extremely high switching speed. It can maintain extremely low switching loss at switching frequency up to 65 kHz. Excellent electrical performance ensures the performance characteristics of the chip and has a very high reliability.

#### 12.8 Protective function

Excellent power systems require sophisticated fault protection to achieve high reliability. The LN9T27DH/EH is designed with a wide range of protection features to meet user requirements including cycle-by-cycle current limiting (OCP), output overload protection (OLP), VDD overvoltage lockout, and under-voltage lockout (UVLO) and Over temperature protect (OTP).

With built-in input voltage compensation technology, the output power is limited to a relatively constant value, which makes the selection of the output rectifier device very easy, and the output diode specifications can be selected more economically to meet a relatively constant output over-current at wide input voltage conditions results in lower system cost.

When the output is overloaded, the FB voltage rises and reaches the set TD\_PL value, the circuit will turn off the MOSFET output, and the system will restart when the VDD voltage drops to the UVLO set point. If the fault does not cancel, the circuit will enter the hiccup protection mode.

After normal operation, VDD is powered by the auxiliary winding of the transformer. If the voltage exceeds the limit voltage, it will be clamped. When the voltage is lower than the UVLO setting voltage, the circuit output will be turned off and the system will be restarted.

## 13. Layout Guidelines

### 13.1 Principles of high-frequency layout

When switching power supply layout should follow the principle of high-frequency layout, where possible, the current loop should be kept to a minimum. It should be advanced and then out of the dual-capacitor and appropriate to maintain a single point of connection capacitance. Three typical current loops are shown in the following figure:

Fig4. Typical current loop diagram

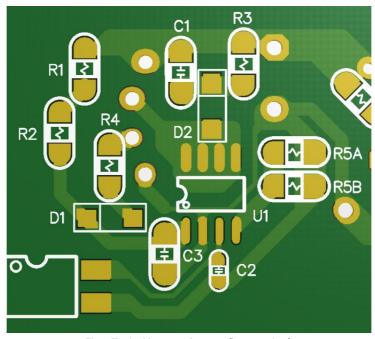

### 13.2 Typical layout reference

An example of a typical PCB layout is shown below.

Fig5. Typical layout reference (bottom view)

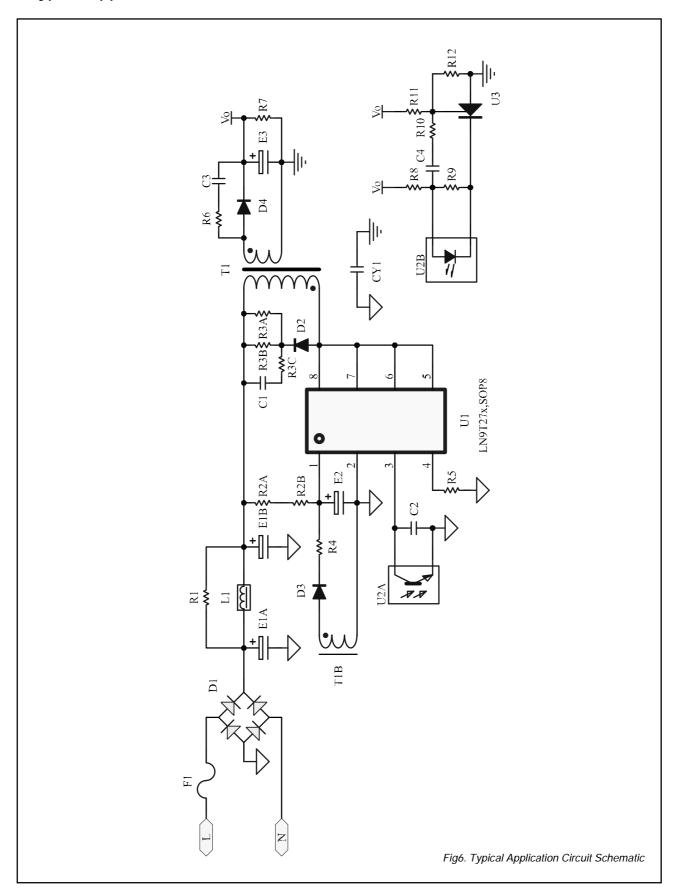

## 14. Typical Application Circuit Schematic (input: 90~265 Vac)

## 15. Mechanical and Packaging

## 16. Orderable Information

| Part No.   | Marking   | MOSFET ID/BVdss | Package | Quantity per Tube |

|------------|-----------|-----------------|---------|-------------------|

| LN9T27DH-T | LN9T27DH  | 64.7007         | SOP8    | 100 PCS/TUBE      |

| LN9T27DH-R | LN9127DH  | 6A 700V         | 3076    | 4000 PCS/REEL     |

| LN9T27EH-T | LNOTOZELI | 04.7001/        | COD9    | 100 PCS/TUBE      |

| LN9T27EH-R |           |                 | SOP8    | 4000 PCS/REEL     |

### 17. Important Notice

力生美, LIISEMI and **?** are trademarks or registered trademarks of LII Semiconductor Inc. No unit, company or individual may use them without written permission. The copyright of the product specifications issued is protected by relevant laws and regulations. All copyrights may not be copied without authorization for any or all of the contents for commercial purposes.

The product specifications are only for the description of the characteristics of the products described, and only for the convenience of using the related products. LII Semiconductor does not undertake to be fully responsible for the errors of the documents, and does not assume any loss caused by the use of this document. In light of the need for product improvement, LII Semiconductor has the right to make necessary changes to this document at any time, and does not undertake any obligation to notify. The English specifications are all translated from the Chinese specifications, and the relevant content is subject to the Chinese specifications.

LII Semiconductor series products have independent patents of related technologies and are protected by relevant laws and regulations. Unauthorized copying, plagiarism or reverse engineering of chips with commercial purposes are not allowed without authorization. LII Semiconductor reserves the right to pursue relevant laws.

LII Semiconductor shall not be liable or jointly liable for any loss caused by the use of related products in life equipment such as medicine and ambulance, unless expressly agreed in the transaction terms.

For the latest information, please visit:

www.liisemi.com